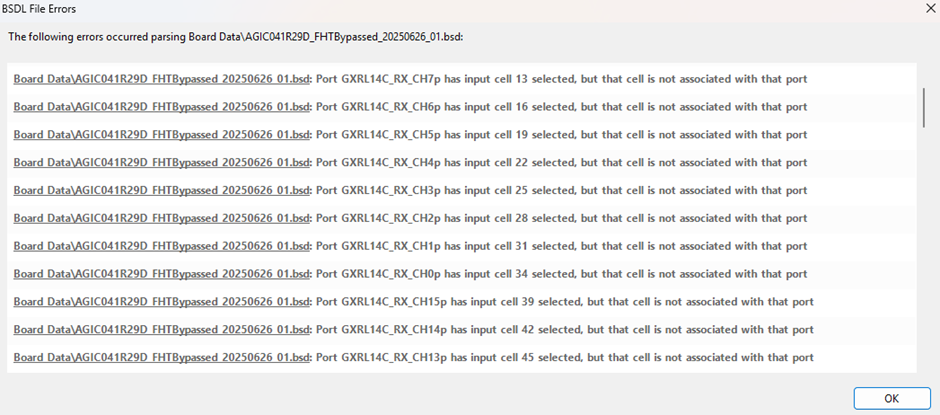

We have recently seen Agilex BSDL files that cause XJDeveloper to emit errors looking like the image below.

The cause of this is a mismatch of information.

Within the BSDL file, in the Advanced I/O description (AIO) section, there is a section that describes the pins’ AC capabilities for IEEE 1149.6 testing. In this section each AC-capable port is defined along with its behaviour:

attribute AIO_Pin_Behavior of Agilex_AGIC041R29D : entity is "GXRL14C_RX_CH7p [13] : LP_time=125.0e-9 HP_time=20.0e-6;"& "GXRL14C_RX_CH6p [16] : LP_time=125.0e-9 HP_time=20.0e-6;"& "GXRL14C_RX_CH5p [19] : LP_time=125.0e-9 HP_time=20.0e-6;"& "GXRL14C_RX_CH4p [22] : LP_time=125.0e-9 HP_time=20.0e-6;"& "GXRL14C_RX_CH3p [25] : LP_time=125.0e-9 HP_time=20.0e-6;"&

The number in square brackets after the port name defines which of the port’s input cells (theoretically there can be more than one) is to be used to read that port. The extract above describes port GXRL14C_RX_CH7p as using input cell 13.

The errors shown in the top picture are due to mismatches between in the list of cell definitions, and the input cell specified in the AIO_Pin_Behavior section of the file. In the boundary register description section of the BSDL file each cell is defined with information on its type, function and the port it is connected to.

-- ******************************************************************* -- * BOUNDARY SCAN CELL INFORMATION * -- ******************************************************************* attribute BOUNDARY_LENGTH of Agilex_AGIC041R29D : entity is 2926; attribute BOUNDARY_REGISTER of Agilex_AGIC041R29D : entity is --BSC group 0 for pin unused pad "0 (BC_4, *, internal, X)," & --BSC group 1 for pin unused pad "1 (BC_4, *, internal, X)," & "2 (BC_4, *, internal, X)," & "3 (BC_4, *, internal, X)," & … … --BSC group 5 for pin GXRL14C_RX_CH7n "13 (BC_4, GXRL14C_RX_CH7n, OBSERVE_ONLY, X)," & …

In this extract from the boundary register description we can see that the boundary cell 13 is associated with port GXRL14C_RX_CH7n. This does not match the description in the AIO_Pin_Behavior section, which states that the positive-leg port of this differential pair GXRL14C_RX_CH7p is linked to cell 13. This mis-match is why XJDeveloper displays the errors seen in figure 1.

How to address these errors

In the IEEE 1149.6 standard the input cell list for an AIO pin is only allowed to list Boundary-Scan Register cells associated with that pin. However, the input cell list is only actually required when a port has more than one input cell associated with it. In this file the ports only have one input cell each, which means the case above can be solved by removing the input cell entirely from the AIO_Pin_Behavior section, as follows:

attribute AIO_Pin_Behavior of Agilex_AGIC041R29D : entity is "GXRL14C_RX_CH7p : LP_time=125.0e-9 HP_time=20.0e-6;"&

This has the added benefit of making the BSDL file more maintainable as the information isn’t repeated in two locations.

XJTAG does not normally recommend modifying BSDL files, because the chip manufacturer should supply files that accurately reflect how boundary scan has been implemented on the silicon in their chip. If you find this issue on one of your Agilex devices we recommend you raise it to Altera/Intel.

Leave A Comment